- Understand the Verilog language and its capabilities for modeling digital systems at various levels of abstraction. The primary focus will be on the RTL level.

- Understand the SystemVerilog language and use its advanced functions to model and simulate complex systems.

- Understand SystemVerilog’s verification capabilities.

- Understand advanced verification techniques for digital systems.

- Know how to use standard verification methodologies.

Contents

- Verilog Fundamentals.

- SystemVerilog for Design.

- SystemVerilog for Hardware Verification.

- Verification Fundamentals.

- Standard Verification Methodologies.

Learning outcomes

Acquire the above skills based on the initial objectives and the proposed content.

Planning

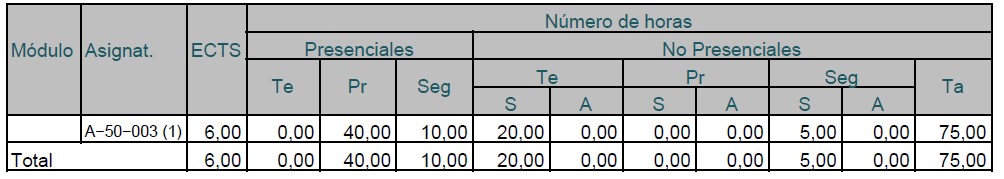

The study planning is shown in the following table:

Te: Theory, Pr: Practice, Seg: Follow-up, Ta: Independent work, S: Synchronous modality, A: Asynchronous modality