Contents

The content covered in this course is as follows:

- Topic 1: Computer Performance and Energy Consumption: Definition of computer performance; Performance metrics; CPU performance equation; Test or benchmarking programs; Power and energy consumption.

- Topic 2: The single-cycle processor: Instruction set format; Data and control paths; Creation of a simple schematic.

- Topic 3: The pipelined processor: Concept of pipelined processing; Pipelined instruction processing; Control in pipelined processing; Data hazards and preemption; Data hazards and blocking; Control hazards and branches.

- Topic 4: Interconnection and I/O: Concept, structure, and types of buses; Single-bus architecture; Bus hierarchy; Bus protocols; I/O system structure; Programmed I/O, using interrupts and based on Direct Memory Access.

- Topic 5: Memory: DRAM memory organization; Memory controller and commands; DRAM temporal parameters; Memory Hierarchy concept; Allocation policies; Replacement policies;

Cache memory performance.

Learning outcomes

The learning outcomes expected after completing this course include:

- Acquiring the aforementioned skills based on the initial objectives and the proposed content.

Planning

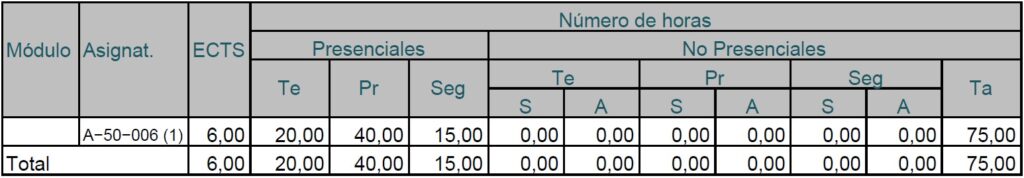

The study planning is shown in the following table:

Te: Theory, Pr: Practice, Seg: Follow-up, Ta: Independent work, S: Synchronous modality, A: Asynchronous modality