- Conocer el leguaje Verilog y sus capacidades para modelar sistemas digitales a varios niveles de abstracción. El enfoque principal estará en el nivel RTL.

- Conocer el lenguaje SystemVerilog y utilizar sus funciones avanzadas para modelar y simular sistemas complejos.

- Conocer las facilidades de SystemVerilog para verificación.

- Conocer técnicas avanzadas de verificación de sistemas digitales.

- Saber utilizar metodologías estándar de verificación.

Contenidos

- Fundamentos de Verilog.

- SystemVerilog para diseño.

- SystemVerilog para verificación de HW.

- Fundamentos de Verificación.

- Metodologías estándar de verificación.

Resultados del aprendizaje

Adquirir las competencias anteriores en base a los objetivos iniciales y el contenido propuesto.

Planificación

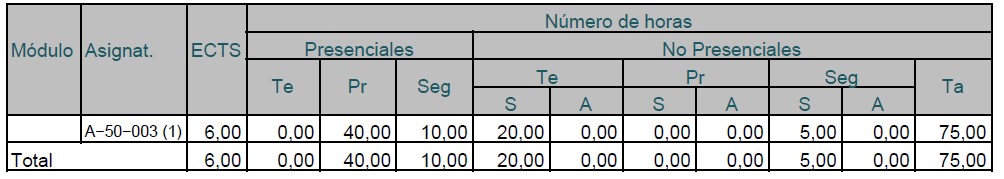

La planificación de los estudios es la que se muestra en la siguiente tabla:

Te: Teoría, Pr: Práctica, Seg: Seguimiento, Ta: Trabajo autónomo, S: Modalidad síncrona, A: Modalidad asíncrona